Kölner Beiträge zur technischen Informatik Cologne Contributions to Computer Engineering Band 1/2024

## Ergebnisse der Workshops 2023 und 2024 des Forschungsschwerpunkts Vernetzte intelligente Infrastrukturen und mobile Systeme (VIMS)

Technology Arts Sciences TH Köln

#### Der Herausgeberkreis des Forschungsschwerpunkts wird gebildet von:

Rainer Bartz Andreas Behrend Andreas Grebe Tobias Krawutschke (Schriftenleitung) Hans W. Nissen Beate Rhein (Schriftenleitung) René Wörzberger (Schriftenleitung) Chunrong Yuan

#### Impressum:

Forschungsschwerpunkt Vernetzte intelligente Infrastrukturen und mobile Systeme Technische Hochschule Köln Fakultät für Informations-, Medien- und Elektrotechnik Betzdorfer Str. 2 D-50679 Köln tobias.krawutschke@th-koeln.de Stand: April 2024 ISSN: 2193-570X

Die Veröffentlichung von Dokumenten über Cologne Open Science erfolgt unter der CC-Lizenz: Namensnennung, keine kommerzielle Nutzung, keine Bearbeitung.

## Inhaltsverzeichnis

| Editorial                                                                                                                                 | 4  |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| A novel approach for the optimal scheduling of a rail network (Tom Wenk, Markus Siebertz, Julian Kartte, Chunrong Yuan)                   | 5  |

| Comparison of Missing Data Imputation Techniques using Autoencoders (Rubaiya Kabir<br>Pranti, Gernot Heisenberg, Sven Woehrle)            | 15 |

| FPGA-based acceleration of neural net simulation (Felix Sebastian Nitz)                                                                   | 19 |

| Improving Traffic Flow Analysis: A Novel Approach to Sound-Based Traffic Density Classi-<br>fication (Leon Schex, Luca Schex)             | 30 |

| Open RAN Threat Analysis of the O-RAN SC Reference Implementation (Henrik Wittemeier,<br>Arn Jonas Dieterich, Andreas Grebe, Thomas Karl) | 37 |

### Editorial

Mit diesem Band im Jahr 2024 wird die Veröffentlichung in der Reihe *Kölner Beiträge zur technischen Informatik* nach dem Band 2/2022 fortgesetzt. Die Fakultät für Informations-, Medien- und Elektrotechnik am Institute of Computer and Communication Technology (ICCT) ermöglicht Master Studierenden nicht nur aus dem Bereich der technischen Informatik eine Möglichkeit Ihre Forschung zu veröffentlichen, die im Rahmen von Forschungs- und Entwicklungsprojekten an der TH Köln und/oder bei Projektpartnern entstand.

Ziel ist es, die Ergebnisse laufender Arbeiten aus den Forschungs- und Entwicklungsaktivitäten des Forschungsschwerpunkts nach außen zu kommunizieren und Informatiker:innen und Informationstechniker:innen außerhalb des Forschungsschwerpunkts z.B. aus dem Kölner Raum einzuladen, neue Ergebnisse aus Wissenschaft und technischer Anwendung im Rahmen von *Cologne Open Science* zu publizieren.

In zwei Workshops wurden die hier veröffentlichten Themen diskutiert. Am 16.6.2023 wurden A novel approach for the optimal scheduling of a rail network (Tom Wenk, Markus Siebertz, Julian Kartte, Chunrong Yuan) und Comparison of Missing Data Imputation Techniques using Autoencoders (Rubaiya Kabir Pranti, Gernot Heisenberg, Sven Woehrle) vorgestellt. Am 15.3.2024 wurden FPGA-based acceleration of neural net simulation (Felix Sebastian Nitz), Improving Traffic Flow Analysis: A Novel Approach to Sound-Based Traffic Density Classification (Leon Schex, Luca Schex), und Open RAN Threat Analysis of the O-RAN SC Reference Implementation (Henrik Wittemeier, Arn Jonas Dieterich, Andreas Grebe, Thomas Karl) vorgestellt.

Der Herausgeberkreis freut sich, diesen neuen Band der Reihe der Fachöffentlichkeit zur kritischen Prüfung und zur möglichen Mitwirkung vorlegen zu können.

Rainer Bartz Andreas Behrend Andreas Grebe Tobias Krawutschke Hans W. Nissen Beate Rhein René Wörzberger Chunrong Yuan

## A novel approach for the optimal scheduling of a rail network

Tom Wenk, Markus Siebertz, Julian Kartte TH Köln - University of Applied Sciences Cologne, Germany

$\{tom\_frederik.wenk,\ markus.siebertz,\ julian\_alexander.kartte\} @smail.th-koeln.de$

Abstract—Creating optimal timetables for passenger transport in a network of railway systems is a well-known but not fully solved problem. In this work, we propose an approach capable of reducing passenger delays and thus ensuring customer satisfaction for networks of arbitrary configurations with different parameters regarding passengers, trains, lines and stations. The approach has been compared to three other ones and evaluated based on the criteria of robustness and quality. The proposed scheduling algorithm performs best on both metrics. It has been shown through experimental study that for a wide variety of different scenarios, our approach can provide high quality timetables with minimal delays.

Index Terms—railroad network, timetable optimization, scheduling strategy, InformatiCup, round-based model

#### I. INTRODUCTION

In 2021, Deutsche Bahn introduced the Deutschlandtakt, a concept toward coordinated scheduling for passenger transport in Germany. It aims at making local public transport in cities and rural areas more attractive. The main idea is to interlock different schedules and make smart and coordinated planning of different travel requests so as to reduce the travel time and minimize the overall delay as well as waiting times in a network system.

In 2022, the German Society for Computer Science organized a coding competition called InformatiCup that tackled this problem of creating optimal timetables for a rail network [1]. The goal of the contest was to minimize the overall delay of all passengers and thus improve customer satisfaction with rail transportation. This so simply formulated task contains a lot of challenges: thousands of passengers want to be transported from start to destination every day, as quickly as possible. However, only a limited number of trains are available to transport these passengers. A huge rail network connects all cities with each other. Smooth operation of all rail vehicles must be ensured to make optimum use of resources.

Clearly, this kind of logistic optimization problem is faced not only by railroad companies, but also by many other logistics companies and organizations involving transportations of people or goods. The algorithmic core of this InformatiCup challenge is thus relevant in an economic context on a daily basis. And an optimal solution to it can be applied to many areas in our modern society, where all resources should be used efficiently and carefully. According to the requirement of InformatiCup, the railroad network is represented as a round-based model. The four elements of it are station, line, train and passenger. A round is a fictive time unit and stands for the shortest interval for action scheduling within the network. Each of the four elements has certain features, as will be detailed in the following paragraphs.

Chunrong Yuan

Autonomous Systems Lab

TH Köln, Cologne, Germany

chunrong.yuan@th-koeln.de

At a station, passengers can get on and off a train as well as stay for any amount of time. A station can only hold a maximum number of trains simultaneously and hence has a train capacity. However, a station does not need to have a passenger capacity, as train stations in Germany are generally not overcrowded.

Every **line** connects bidirectionally two stations and it is guaranteed that all stations are directly or transitively connected by lines. Each line can accommodate a certain number of trains. The length of the lines influences the travel time of trains. The exact position of the trains on the track is irrelevant for the underlying task.

Every train can transport up to a maximum number of passengers with a certain velocity on lines between stations. Passengers cannot board (or leave) a train in the round of its departure (or arrival). If a train starts on a line, it cannot execute another action, until it reaches the next station. By multiplying the passed number of rounds on the current line with the speed of the train, one gets the (fictive) distance it has travelled. The train arrives at the next station in the round in which the distance travelled on the current line is greater than or equal to the length of the line. The train will then inevitably stop at this station and passengers get the possibility to board or leave the train. It can happen that a train arrives at the next station in the same round in which it has departed from the previous station. Each train is allocated to a given start station. In case no specific starting station is yet assigned to a train, which will be referred to as having an arbitrary starting station in the following, a suitable station will be determined for it.

**Passengers** are not modelled individually. They are grouped together and each group represents all the members travelling together from a start station to a destination. The size of a group should be equal or greater than one. Additionally, for every passenger group, a desired arrival time is defined in the input. This is later used to calculate the delay and therefore the quality of the algorithm. If passengers arrive at their destinations later than the desired arrival time, they are delayed. The goal is to generate a timetable leading to no or minimal passenger delay. For each passenger group, the delay  $p_{\text{delay}}$  is calculated as the difference between the actual and desired arrival time at destination. The overall delay  $d_{\text{total}}$  is the sum of the delays for all passengers, which is calculated by Eqn. 1 and 2.

$$d_{\text{total}} = \sum_{p \in P} p_{\text{delay}} \tag{1}$$

$$p_{\text{delay}} = \begin{cases} p_{\text{at}} - p_{\text{dt}}, & \text{if } p_{\text{at}} > p_{\text{dt}} \\ 0, & \text{else} \end{cases}$$

(2)

If passengers arrive earlier than desired, it is regarded to have no influence on their satisfaction, meaning the delay does not get lowered.

Every train and every group of passengers can execute one action per round. Passengers can either board or leave a train or they can wait at a station or travel on a train. Trains can either wait at a station, wait on a line or execute one of the following moves to drive along the railroad network:

- · Leave a station and start on a line

- Leave a station, start on a line, and arrive at the next station

- Continue driving on a line

• Continue driving on a line and arrive at the next station. Trains are only allowed to leave their current station if they have no passengers that want to board or leave the train.

#### II. RELATED WORK

The train scheduling problem is widely considered as being NP-hard, in some specific problem formulations NP-complete, and very complex to solve. Although the problem was considerably discussed and different methods have been developed for tasks with specific settings [2] [3] [4] [5] [6] [7], none of the available solutions is directly transferable to the problem defined in Section I.

Among the participants of InformatiCup 2022, several teams have made their submissions publicly available. This makes it possible to compare different approaches. In the following, the methods developed by three other teams will be summarized.

#### A. Team ZZE (Zügig zum Erfolg)

The scheduling problem is formulated by ZZE as a variation of the Knapsack problem [8], with the size of passenger groups defined as weight and their desired arrival time as value. While the original problem is intended to maximize a value, ZZE tries to minimize the arrival time of passengers [9].

First, passengers are further grouped into blocks such that each block contains passengers with the same starting station and destination. Each block is then sorted by the desired arrival time in an ascending order. Trains are then assigned to passengers based on their positions and distances to the locations of passengers. Trains that already have a start station are prioritized for a calculation. If there is no train in a station with waiting passengers, a train must be called there to pick up the passengers.

Another criterion for train assignment is to ensure that at least one train whose passenger capacity is equal or greater than the maximal block size is available at a station on the route network. If this is not the case, a train with a sufficient capacity has to be placed at the location of the passenger as soon as possible.

For each passenger and each suitable train, the Dijkstra algorithm [10] is used to calculate the route from the starting station to the destination. Additionally, if a train needs to be called, the time at which that train could start at the starting station of the passenger is determined. Both measures are then used to determine which train would arrive at the destination at the earliest time. Once determined, that train is assigned to the selected group.

If a route or a station is occupied for a certain time, the delay is determined. If a station is occupied for an indefinite period of time, the station is cleared by driving the train out. If a route of a journey can be travelled without problems, this journey is saved permanently and can no longer be changed afterwards. All subsequent assignments must be based on this fixed assignment.

#### B. Team OBO (Off By One)

The team OBO built their solution under the premise that the train scheduling problem is NP-Hard and that there does not exist an optimal solution for the problem [11]. For the purpose of finding an approximation algorithm that can provide a sufficiently good solution, three methods have been taken into consideration:

- Genetic search [12], for reproducing and improving the "fittest" solutions until an optimal solution is found

- Simulated annealing [12], by making random changes to an existing solution and then evaluating its impact based on the quality of the solution

- Tabu-enhanced genetic search [13], by using a tabu-list during search

After evaluation, the Tabu-enhanced genetic search has been adopted by the team OBO, where movements that lead to bad results are stored in a tabu list and omitted from the following iterations. If such movements are found at an early stage, it will help the system arrive faster at a good solution. It can also prevent cyclical behaviour so that the system will not get stuck in suboptimal regions.

#### C. Team HS (HeiSpeed)

Similar to [14], the HS solution [15] is based on the use of an algorithm ensemble, which consists of three algorithms: the Divide-and-Conquer algorithm [16], the Basic Greedy algorithm [10] [12] and the Branch-and-Bound algorithm [17]. The results of these methods are compared and the best solution is chosen among them.

The Divide-and-Conquer method will break down a larger problem into smaller subproblems which can then be solved independently. The advantage of this approach is that it limits

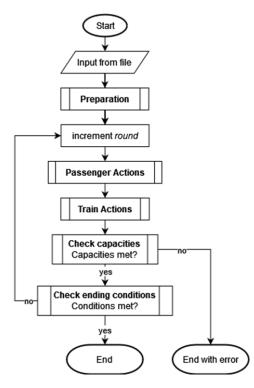

Fig. 1. Overview of the scheduling process.

the risk of overflowing the routes and deadlocks. Computationally intensive operations such as searching for the shortest path within independent blocks become faster due to a reduced problem size. In order to use the Divide-and-Conquer algorithm, shortest paths between stations have to be precalculated so that a balanced partition of the railway network can be achieved. Trains are then assigned on the basis of balanced capacities among stations and routes.

The Greedy approach uses the Dijkstra algorithm to find the shortest path from start to destination for a single group of passengers. This means that it follows a simple resource reservation strategy and cannot reliably prevent deadlocks, as it uses a global iterative approach.

In the case of Branch and Bound, a brute force search is not applied to all possible solutions. By using an upper bound to determine if a solution is promising enough, and a lower bound that approximates the cost, this leads to the reduction of computational costs at an early stage.

#### **III. SYSTEM OVERVIEW**

The approach proposed in this work aims at the construction of optimal timetables for arbitrarily configured networks. It consists mainly of processing rules and scheduling strategies designed for a preparation phase and an iterative round-based phase, as is shown in Fig. 1.

Two kinds of tasks are involved in the preparation phase. One is the construction of a connected bidirectional graph

| Variable                      | Description                                 |  |  |

|-------------------------------|---------------------------------------------|--|--|

|                               |                                             |  |  |

| Train $t \in T$               | Train entity                                |  |  |

| $t_{cap}$                     | Capacity of a train regarding passengers    |  |  |

| $t_{\rm pas}$                 | All passenger groups on a train             |  |  |

| $t_s$                         | Speed of train                              |  |  |

| $t_l$                         | Location of train (line or station id)      |  |  |

| $t_d$                         | Destination of train                        |  |  |

| $t_{\rm route}$               | Route of train                              |  |  |

| $t_{ m blocked}$              | Trains performing certain actions           |  |  |

| Line $l \in L$                | Line entity                                 |  |  |

| lcap                          | Line capacity regarding trains              |  |  |

| l <sub>trains</sub>           | All trains on a line                        |  |  |

| $l_l$                         | Length of line                              |  |  |

| $l(s_0, s_1)$                 | Line that connects stations $s_0$ and $s_1$ |  |  |

| Station $s \in S$             | Station entity                              |  |  |

| s <sub>cap</sub>              | Station capacity regarding trains           |  |  |

| strains                       | All trains in a station                     |  |  |

| $s_{\rm pas}$                 | All passengers at a station                 |  |  |

| Group of passengers $p \in P$ | Passenger group entity                      |  |  |

| $p_l$                         | Location of passenger group                 |  |  |

| $p_d$                         | Destination of passenger group              |  |  |

| $p_s$                         | Size of passenger group                     |  |  |

| $p_{\mathrm{at}}$             | Actual arrival time at destination          |  |  |

| $p_{\rm dt}$                  | Desired arrival time at destination         |  |  |

| $p_{\text{delay}}$            | Delay of passenger group                    |  |  |

TABLE I ENTITIES AND THEIR ATTRIBUTES

for the representation of a rail network having an arbitrary configuration. The other contains the initializations of the four elements of a rail network together with their attributes using a standardized format, where a number of entities relating to trains, passengers, lines and stations are set up properly. All the entities and attributes are listed in Table 1.

Once the initializations are performed, a structural model is built which is capable of converting task scenarios with arbitrarily configured rail networks into a proper representation. The model consists of a compact data structure with features related to the underlying scheduling tasks and a graph representation of the network. With the features of these entities initialized properly, they can then interact with each other in the iterative scheduling phase: trains can pick up passengers and will then iteratively transport the passenger with the highest priority to its destination.

In order to achieve an optimal solution for a task scenario, it is important to set passenger priority and to assign trains to a properly selected start station. Both are determined during the initialization process as well. Details on the preparation and initializations regarding these two aspects will be discussed in Section IV. In Section V, strategies dealing with the iterative scheduling process will be presented.

#### IV. GRAPH CONSTRUCTION AND INITIALIZATIONS

Before the round-based part of the algorithms begins, a connected bidirectional graph G is constructed that represents the relations between stations and lines. The graph is later used to find the shortest path between two stations. It consists of a set of nodes representing the stations and a set of edges representing the lines. The cost of each edge is equivalent to its length.

Passenger groups are then allocated to their individual starting stations in the graph. Based on the desired arrival time, passengers are sorted in an ascending order, leading to an ordered set of passengers shown in Eqn. 3:

$$O_{\text{pas}} = \{ p_0, p_1, \dots, p_n \mid p_{i_{dt}} \le p_{(i+1)_{dt}}, \ 0 \le i \le n-1 \}$$

(3)

This process also functions as a prioritization of passengers. The earlier the desired arrival time of a passenger group, the higher its priority and the sooner it will be handled in the round-based phase.

Trains are allocated to their individual starting stations in the graph as well. An ordered set of trains is constructed, by sorting the speed of each train in a descending order.

$$O_{\text{trains}} = \{t_0, t_1, \dots, t_n | t_{i_s} \ge t_{i+1_s}, \ 0 \le i \le n-1\}$$

(4)

For trains with an arbitrary starting station, they have to be assigned to a station  $s^{\alpha} \in S$  that fulfills these conditions:

$$|s^{\alpha}|_{\text{pas}} > 0 \tag{5}$$

$$(s^{\alpha})_{\rm cap} - |s^{\alpha}|_{\rm trains} > 0 \tag{6}$$

$$\nexists s \in S - s^{\alpha} : s_{rp} \le (s^{\alpha})_{rp} \tag{7}$$

$$s_{rp} = |s|_{\text{pas}} - \sum_{t \in s_{\text{trains}}} t_{\text{cap}} \tag{8}$$

As determined by the conditions shown in Eqn. 5 to 8, such a train will get allocated to a station  $s^{\alpha}$  that:

- has passengers, as determined by Eqn. 5;

- can accommodate the additional train (i.e., station capacity is bigger than the number of trains at station s<sup>α</sup>), which is decided by Eqn. 6;

- has the highest need for additional trains, i.e., has the biggest number of passengers who are waiting to be transported, which is determined by Eqn. 7 and 8.

The the number of waiting passengers at a station s is estimated as the difference between the number of passengers at station s and the number of passengers that could be held by existing trains at s.

If no station exists that meets all these conditions, the train can be allocated to a station s with no passenger. But still smust satisfy the conditions specified in Eqn. 6 to 8. Fig. 2 shows the above initializations performed in the preparation phase. The step of assigning a proper starting station for a train is shown on the bottom right part of Fig. 2.

#### V. ITERATIVE ROUND-BASED SCHEDULING

Our round-based scheduling approach deals with the determination of actions and routes for passengers based on the graph model and entities initialized in Section IV. In each round, passenger and train actions have to be decided properly. These actions have to be executed in a sequence such that in the end, all passengers will arrive at their desired destinations and the delay over all passengers is minimized.

After each round, it is checked whether all passengers have arrived at their destination station, determined by Eqn. 9:

Fig. 2. Initializations during the preparation phase.

$$\forall p \in P : p_l = p_d \tag{9}$$

Once this condition is met, the algorithm will end successfully. If this is not the case, the following conditions shown in Eqn. 10 to 12 will be checked:

$$\forall s \in S : s_{\text{cap}} \ge |s_{\text{trains}}| \tag{10}$$

$$\forall t \in T : t_{\text{cap}} \ge |t_{\text{passengers}}| \tag{11}$$

$$\forall l \in L : l_{can} > |l_{trains}| \tag{12}$$

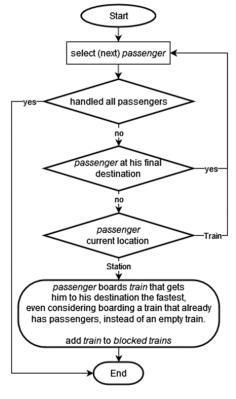

#### A. Passenger actions

In every round, the algorithm iterates through all passengers. Each passenger  $p \in P$  executes one action depending on its current location  $p_l$ . Passengers on trains and passengers waiting at stations will perform different actions (see Fig. 3).

For a passenger p on a train t, possible actions are simply staying on it or getting off if the current location of the train is the same as the desired destination, i.e.  $t_l = p_d$ .

If a passenger p with  $p_l \neq p_d$  is waiting at a station s, every train in station s will be checked to determine whether it satisfies the following condition:

$$p_s \le t_{\rm cap} - \sum_{p_k \in t_{\rm pas}} p_k \tag{13}$$

Fig. 3. Passenger actions.

The goal is to find candidate trains that are located at station s and whose remaining capacity is not smaller than the group size of p so that it has enough capacity left to accommodate this passenger group. If no train meets these conditions, then p must wait. Otherwise, the task becomes the selection of a train from all those candidate trains so that passenger p can get on it.

For each train among these candidates, we estimate a possible arrival time  $p_{est}$  for passenger p. The train with the least delay for all onboard passenger groups will be chosen. In case the candidate train t has yet no passenger onboard, then p would be the only passenger which also has the highest priority on this train. The estimated arrival time  $p_{est}$  can be calculated as the travel time from the current station to the destination of p on the shortest route. And the delay of selecting this route is  $p_{est} - p_{dt}$ , as the decision has no influence on other passengers and  $p_{est}$  is the earliest possible time it would take train t to drive from  $p_t$  to  $p_d$ .

If one or more passengers are already on the train t, and t is currently scheduling along a route  $t_{route}$  toward the destination of an onboard passenger group with the highest priority, then there are two possibilities. If the current route  $t_{route}$  would later pass  $p_d$ , then  $p_{est}$  can be determined as the number of rounds it takes the train t to drive from  $p_l$  to  $p_d$  along  $t_{route}$ . If  $p_d$  is not a station on the current route of the train t, a balance must be struck between conflicting consequences. If we let passenger p board the train t and satisfy its need first so that p could travel to the desired destination  $p_d$  as quickly as possible. However, all other passengers who are already on the train will be delayed by the boarding of p, since the train must stop at an extra station  $p_d$ , leading to an increased delay for all passengers on the train.

In order to be able to weigh up among different options, the delay for each passenger  $p_i$  on train t is estimated and all delays are summed up to  $d_t$ , as is shown in Eqn. 14 and 15.

$$d_t = \sum_{i=0}^{n} (p_{i_{\text{est}}} - p_{i_{\text{dt}}})$$

(14)

$$p_{i_{est}} = \begin{cases} \tau_t(t_l, p_{i_d}), & \text{if } i = 0\\ p_{(i-1)_{est}} + \tau_t(p_{(k-1)_d}, p_{k_d}), & \text{else} \end{cases}$$

(15)

In Eqn. 15,  $\tau_t(s_1, s_2)$  represents the time (i.e., number of rounds) it takes t to drive from  $s_1$  to  $s_2$ . And the estimated arriving time for passenger p corresponds to the case i = 0. All passengers already onboard correspond to cases with i > 0.

Based on the calculated total delay  $d_t$  for each candidate train, an optimal solution can be found among all of them by selecting the train with the minimal total delay for all involved passengers.

Boarding a train will prevent that train from performing further actions in the current round, i.e., it belongs now to a set of blocked trains, the  $t_{blocked}$ . If the passenger group is not able to find a suitable train in the current round, it must wait for the next round. Since passengers are sorted by their desired arrival time, the iterative process ensures that passengers with higher priority will board the most suitable trains first.

Like boarding, leaving a train prevents that train from performing further actions in the current round.

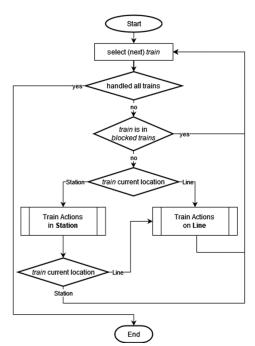

#### B. Train actions

í

Once all passengers have executed an action, actions for individual trains will be determined based on its current location. The overall process of train activities is illustrated in Fig. 4. Since trains located at stations should perform different actions as trains that are driving on lines, details regarding the determination of train activities in both cases are further illustrated in Fig. 5-6 and Fig. 7, respectively.

For each train located at a station, it is necessary to determine its destination  $t_d$  together with a route  $t_{\text{route}}$ . This process depends on whether the train has passengers on board or not.

In case a train t at a station has passengers, i.e.,  $|t_{\text{pas}}| \neq \emptyset$ , the onboard passengers are sorted by their desired arrival time, leading to a sorted set  $t_{\text{pas}}$ , as is shown in Eqn. 16.

$$t_{\text{pas}} = \{ p_0, p_1, \dots, p_n \, | \, p_{i_{\text{dt}}} \le p_{(i+1)_{\text{dt}}}, 0 \le i \le n-1 \}$$

(16)

The destination of train t is set to the destination of the passenger with the lowest desired arrival time, resulting in

$$t_d = \left(p_0\right)_d\tag{17}$$

Fig. 4. Train actions.

Fig. 5. Determine actions for trains at stations.

Fig. 6. Determining routes for trains located at stations.

This means, the lower the arrival time, the higher the priority, and the sooner the passenger gets handled and arrives at the destination. Once the destination is set, the Dijkstra algorithm is used to find the shortest path from  $t_l$  to  $t_d$  in the constructed graph G.

For each train at a station, an optimal route  $t_{\text{route}}$  is set to the one that takes train t the smallest number of rounds to get from  $t_l$  to  $(p_0)_d$ , as is formulated as Eqn. 18:

$$t_{\text{route}} = \{s_0, s_1, \dots, s_n \,|\, s_n = (p_0)_{\mathsf{d}}\} \tag{18}$$

Once the route is set for the train t at a station  $t_l$  with  $t_l \in S$ , it checks the lines that are adjacent to  $t_l$  and chooses the line  $l(t_l, s_0)$  that would bring it to the next station on  $t_{\text{route}}$ . Then train t will start on l, where the condition regarding the remaining capacity of the line is met:  $l_{\text{remcap}} = l_{\text{cap}} - l_{\text{trains}} \ge 1$ . Once the train t has executed this action, it is moved to  $t_{\text{blocked}}$ , meaning a new action for it will not be allowed until the next round.

If the line has no more capacity to hold train *t*, this means the network has a local bottleneck, which has to be dealt with properly.

As is illustrated on the right part of Fig. 5, a possible solution to such kind of bottleneck will be the search for another train  $t_{\text{temp}}$  which is currently driving on the line and could make room for train t so that t could start on the line and  $t_{\text{temp}}$  would stop temporarily at station  $t_l$ . Suppose there exists a train  $t_{\text{temp}}$  which is heading toward the station  $t_l$ . If the train  $t_{\text{temp}}$  has not yet executed an action in the current round, it will arrive at station  $t_l$  in this round and then be

able to swap places with train t. After that, both trains will be moved to  $t_{\rm blocked}$ .

If there does not exist a train  $t_{\text{temp}}$  that meets the above condition, then train t must wait at station  $t_l$ . In the next round, it has to search again for the possibility of making a swap operation.

In the simple case that train t at station  $t_l$  has no onboard passenger, i.e.,  $|t_{\text{pas}}| = \emptyset$ , it will check whether there are passengers who need to be picked up at other stations, as is shown in Fig. 6. A sorted set of waiting passengers at other stations whose boarding on train t would not violate its capacity can be obtained based on Eqn. 19:

$$P_{w} = \{p_{0}, p_{1}, \dots, p_{n} \mid p_{i_{l}} \neq t_{l}, p_{i_{s}} \leq t_{cap}, p_{i_{dt}} \leq p_{(i+1)_{dt}}\}$$

(19)

If  $P_w = \emptyset$ , the train just waits at its current station. If such a set of waiting passengers  $P_w$  does exist, the destination of train t will be set to the location of passenger  $p_0 \in P_w$  with the lowest desired arrival time so that  $t_d = p_{0l}$ . A route for train t is then determined by the Dijkstra algorithm, leading to  $t_{\text{route}} = \{s_0, s_1, \dots, p_{0l}\}$ .

The above process is repeated in each round so that  $t_{\text{route}}$  can be adjusted dynamically based on the current situations, making it possible to deal with changes or disturbances occurred in the network.

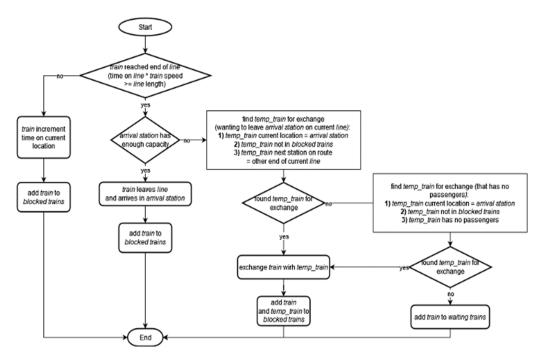

Until now we have put forward several strategies toward iterative action generations for trains that are located at stations. Of course, trains can also be already driving on lines. Fig. 7 shows how actions can be generated for these running trains.

For each train t driving on a line, we have  $t_l \in L$ . In each round, it is necessary to check whether the train should keep driving on its current line or stop. Suppose  $C_t^l$  is the number of rounds the train has already spent on the line, then the stop condition is:  $C_t^l \cdot t_s \ge l_{t_l}$ , where  $t_s$  is the speed of the train t and  $l_{t_l}$  is the length of the line.

If the stop condition is not met, the train simply continues driving on the line,  $C_t^l$  is incremented by 1, and t is added to  $t_{\text{blocked}}$ .

If a train reaches its end station  $s_e$  on the line, the capacity of  $s_e$  has to be checked. If  $s_{e_{cap}} - |s_{e_{trains}}| \ge 1$ , the train can enter the station, and it is added to  $t_{\text{blocked}}$ . Otherwise, there is a bottleneck situation at station  $s_e$ . This has to be treated again with a swap operation. Here there are two possibilities: One way is to find a train which is about to leave station  $s_e$ , the other is to find a train in station  $s_e$  that has no passengers onboard.

For the former case, a train  $t_{\text{temp}}$  that fulfills the following conditions will be looked for:

$$t_{\text{temp}_l} = s_e \tag{20}$$

$$t_{\text{temp}_{route}} = \{s_e, s_1, \dots, s_n\} \neq \emptyset$$

(21)

$$t_{\text{temp}} \notin t_{\text{blocked}}$$

(22)

If such a train cannot be found, another search will be carried out, by trying to find a train  $t_{temp}$ , where the following conditions shown in Eqn. 23-25 are met:

$$t_{\text{temp}_l} = s_e \tag{23}$$

$$|t_{\text{temp}_{nas}}| = 0 \tag{24}$$

$$t_{\text{temp}} \notin t_{\text{blocked}}$$

(25)

If one of the above searches is successful, a swap action will be executed. Then t and  $t_{\text{temp}}$  will be added to  $t_{\text{blocked}}$ . Otherwise, train t has to wait until the next round.

#### VI. EXPERIMENTAL EVALUATION

The proposed approach has been experimentally evaluated using test data containing various network configurations. In order to test the proposed approach under more difficult conditions than those provided by the InformatiCup, we have realized an automatic data generator. Based on this extended data set, a comparative study has been carried out.

#### A. Test data and data generator

Each piece of test data consists of a network configuration with an arbitrary set of trains, stations, lines, and passengers, formatted according to the specification of InformatiCup and stored in a file. An example is shown in Fig. 8. It can be observed that for a train whose starting station is not yet set, there is an asterisk (\*) shown directly beside the train, as is the case of train T2.

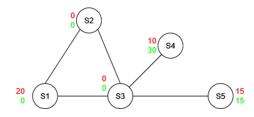

Using our algorithm explained in Section IV, a graph with nodes and edges can be constructed. For a test scenario with five stations, the constructed graph is visualized in Fig. 9, where the number of passengers waiting at each station is shown in color red. Shown in color green are the maximal numbers of trains that can be held at individual stations.

According to our algorithm designed for the preparation phase, a train with an arbitrary starting station will be assigned to station  $s_1$ . It has the highest need for additional trains, with twenty groups of waiting passengers, as is shown in Fig. 9.

The initial test data are provided by the organizing society and a few attending teams of the InformatiCup. The original data set contains only a small number of test cases, with few of the test scenarios having more than a hundred elements.

For the automatic generation of test data with larger numbers of elements and more complex configurations, we have built a data generator, where a Python script has been written so that additional test scenarios can be created on the fly. In an interactive process, all the necessary parameters that a test scenario must contain, as is regulated in the specification of the InformatiCup, can be instantiated through user input.

Using the data generator, those attributes  $t_{cap}$ ,  $s_{cap}$ ,  $l_{cap}$ ,  $p_s$ ,  $t_s$ ,  $l_l$  can be initialized randomly. The number of trains with an arbitrary starting station can be set randomly as well. Random values can also be generated for setting the starting stations for both passengers and trains.

In order to ensure that the generated network was connected, the data generator will first create all possible lines among the stations. Then it will repeat a process, where in each iteration, a line is randomly removed while keeping the graph connected.

Fig. 7. Determine actions for trains driving on lines.

# Stations: str(ID) # Stations [Stations] S1 2 S2 2 S3 2 # Lines: str(ID) str(start station) str(end station) dec(length) int(capacity)

[Lines]

L1 52 53 3.14 1

L2 52 51 4 1 # Züge: str(ID) str(start station)/\* dec(speed) int(capacity) [Trains] T1 52 5:5 30 T2 \* 0.9999999 50 # Passagiere: str(ID) str(start station) str(end station)

# int(group size) int(desired arrival time)

# Int(group 3. [Passengers] P1 S2 S3 3 3 P2 S1 S1 10 4

Fig. 8. Example of a network configuration.

Fig. 9. Visualization of the constructed graph.

The iterative process stops when the desired number of lines was reached.

In order to ensure that a test scenario will definitely result

TABLE II NETWORK CONFIGURATIONS OF EIGHT SELF-GENERATED TEST CASES

| Stations | Passengers | Trains | Lines | Total |

|----------|------------|--------|-------|-------|

| 6        | 7          | 5      | 10    | 28    |

| 11       | 15         | 8      | 31    | 65    |

| 19       | 32         | 12     | 97    | 160   |

| 33       | 68         | 18     | 301   | 420   |

| 57       | 143        | 27     | 934   | 1161  |

| 97       | 301        | 41     | 2896  | 3335  |

| 165      | 633        | 62     | 8978  | 9838  |

| 281      | 1330       | 93     | 27832 | 29536 |

in delay, a few test scenarios have been constructed in such a way that it will enforce a delay. This was achieved by setting the desired arrival time for each passenger to a value only achievable by the fastest train available in the network. This will definitely lead to delay for some passengers who have to travel with a slower train. In the following, these so generated test data will be referred to as delay-enforcing ones.

A total of 67 test cases have been used for the purpose of comparative study, where our approach has been compared with the three algorithms introduced in Section II. Within the total test data, eight cases have been constructed with the technique of delay enforcing. The relevant parameters involved in these eight cases are shown in Table II, where each row stands for one test case. From top to bottom, one can observe an exponentially enlargement of network complexity, which is due to the rapid increase in the number of total elements within the network.

Fig. 10. Robustness and quality comparison.

#### B. Comparative study

A comparative study has been carried out, involving the performance evaluation of four approaches using two evaluation criteria: one is robustness, and the other is quality. Here, robustness describes the proportion with which an algorithm returns a valid passenger timetable and train timetable. The timetables are defined as valid if they conform to the formalized format described in [1]. The quality of an algorithm depends on the delay over all passengers, i.e.,  $d_{total}$ .

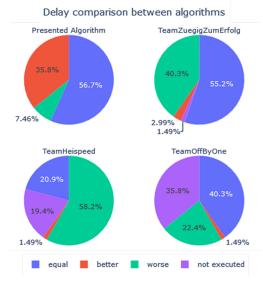

As demonstrated in Fig. 10, the presented algorithm constructs valid timetables for all the test cases, reaching a robustness of 100%. Team ZZE achieved a robustness of 98.5%, only failing to return valid timetables for one test case. The algorithm from team OBO did not return timetables for 24 cases, resulting in a robustness of 64.2%. Team HS achieved a robustness of 80.6%.

For each algorithm and each input test case, the delay over all passengers has been calculated from the corresponding passenger timetable. The quality was then labelled as better, equal, worse, or not executed, based on the criteria described in Table III.

The distributions of the quality labels are displayed for each algorithm in Fig. 10 as well. The proposed algorithm achieved the highest quality on 35.8% of the test cases and a quality equal to the highest quality of the other three algorithms in 56.7% instances. This means that the presented algorithm was not among the best algorithms in only 7.46% of the time. Team ZZE performed best on two cases and was among the best in 55.2% of all test scenarios. The algorithm performed worse on 40.3% of the inputs. Team HS and team OBO both achieved the highest quality on one test case and were among the best algorithms in 20.9% and 40.3% instances, respectively. Team

TABLE III QUALITY LABELS BASED ON PERFORMANCE COMPARISON

| Quality labels | Performance compared among the four algorithms            |

|----------------|-----------------------------------------------------------|

| Better         | The algorithm achieved the highest quality on the input   |

| Equal          | No other algorithm achieved a higher quality on the       |

|                | input, but at least one other algorithm achieved the same |

|                | quality                                                   |

| Worse          | At least one other algorithm achieved a higher quality    |

|                | on the input                                              |

| Not executed   | The algorithm was not able to return valid timetables     |

|                | for the input                                             |

TABLE IV Total delay rendered by the four scheduling algorithms

|        | Presented Algorithm | Team HS | Team ZZE | Team OBO |

|--------|---------------------|---------|----------|----------|

| Mean   | 13.275              | 1610.5  | 20.55    | 23.95    |

| Median | 0                   | 3       | 0        | 0        |

| Min    | 0                   | 0       | 0        | 0        |

| Max    | 400                 | 60319   | 653      | 715      |

| Sum    | 531                 | 64420   | 822      | 958      |

HS performed worse on 58.2% of the inputs, team OBO on 22.4% of the inputs.

It should be noted that a lot of the test cases were constructed in a way such that an overall delay of zero, i.e.,  $d_{\text{total}} = \sum_{p \in P} p_{\text{delay}} = 0$ , could be achieved easily, which explains the high occurrences of the quality label "Equal".

Excluding inputs for which at least one of the algorithms failed to create a valid timetable, one obtains the values of total delays achieved by the four algorithms, as is displayed in Table IV. Among these inputs, the presented approach has outperformed the other three, achieving the shortest delay with the lowest values regarding all the measures including mean, median, minimum, and maximum and sum. Team ZZE achieved the second lowest values, followed by team OBO. Compared to these three teams, the team HS achieved a substantially longer delay with particularly larger values regarding the mean, sum, and maximum measures.

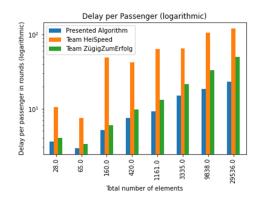

The results achieved by three of the four algorithms on the delay-enforcing data are illustrated in Fig. 11. Here team OBO

Fig. 11. Delay per passenger on delay-enforcing data.

was excluded in the graphic, as it could not provide valid timetables in 7 out of 8 cases. The proposed approach delivers the timetables with the highest quality for each test instance, followed by team ZZE. Team HS achieved a considerably longer delay on all eight cases.

#### VII. CONCLUSION

We have developed an approach for train scheduling with the goal of solving the 2022 InformatiCup challenge. The approach has been validated not only with test scenarios defined by the original InformatiCup but also with more complex scenarios having much more complicated network configurations and conditions. The proposed approach has achieved the highest robustness, and for most test scenarios, the highest quality among all the compared algorithms. Through experimental study, it has been demonstrated that the proposed scheduling strategies designed for an arbitrarily set of passenger requests in different configurations of network resources (i.e., a network with trains and lines) can achieve a comparatively low delay for all passengers.

Using the proposed approach, it is possible to deliver satisfactory timetables for a network of rail transportation systems. Another algorithmic advantage lies in its flexibility and adaptability. If the network configuration has been changed, it is possible to generate an updated timetable with minimal delay while accommodating dynamic variations for trains and passengers within the network. This is due to the fact that during the iterative scheduling phase, passenger and train actions are determined dynamically, by applying the same principle for the minimization of the overall delay.

It should be noted that in the current design of round-based iterations, the assignment of round has an abstract nature, since the line length, the train speed, and the time are given in fictive units. However, the use of rounds can be applied in the real world as well, where metric units (e.g., kilometres per hour) are used instead. While one round could be equivalent to any amount of time, its value should be chosen properly, as a balance must be struck: on the one hand, choosing a shorter time interval for one round would lead to a scheduling result with higher quality; on the other hand, it would require that

scheduling decisions have to be made more frequently, which would lead to a higher consumption of computation time and resources.

#### REFERENCES

- [1] "InformatiCup 2021 Abfahrt!," 2021. [Online]. Available: https:// github.com/informatiCup/informatiCup2022

- K. Ghoseiri, F. Szidarovszky and M. J. Asgharpour, "A multi-objective train scheduling model and solution," Transportation, 2004, pp. 927–952. [2] [3] X. Cai and C.J. Goh, "A fast heuristic for the train scheduling problem,"

- [4] X. Cat and C.J. Son, A fast neuristic for the train scheduling protein, Computers & Operations Research, Vol. 21, 1994, pp 499-510.

[4] X. Li, D. Wang, K. Li, Z. Gao, "Green train scheduling model and fuzzy multi-objective optimization algorithm," Applied Mathematical Modelling, vol. 37, no. 4, 2013, pp. 2063–2073.

- Y. Wang, "Passenger-demands-oriented train scheduling for an urban rail [5] transit network," Transportation Research Part C: Emerging Technologies, vol. 60, 2015, pp. 1-23.

- L. Yang, J. Qi, S. Li and Y. Gao, "Collaborative optimization for train [6] scheduling and train stop planning on high-speed railways," Omega, vol. 64, 2016, pp. 57–76. [7] X. Xu, K. Li, and X. Li, "A multi-objective subway timetable optimiza-

- tion approach with minimum passenger time and energy consumption," Journal of Advanced Transportation, vol. 50, no. 1, 2016, pp. 69-95.

- S. Martello, "Knapsack problems: algorithms and computer implemen-B. Ünal, H. Yang, L.H. Hsu and L. Dreyer, "Team Zügig zum Erfolg -

- [9] Project Report," 2022. [Online]. Available: https://drive.google.com/file/ d/1MlNx56C3BgLioU3\_gALE6AEKQRJX3vcb/view?usp=share\_link.

- [10] E. W. Dijkstra, "A note on two problems in connexion with graphs," Numer. Math. 1, 1959, pp. 269–271.

[11] L. Carstens-Behrens and O. Herrmann, "An Application Of Tabu-Enhanced Genetic Search To A Railway Optimization Problem," 2022. [Online]. Available: https://drive.google.com/drive/folders/ 1oYtIKKOKqyTLJL1nZQeGhl97w6LFdPCq?usp=share\_link.

- [12] S.J. Russell and P. Norvig, "Artificial intelligence: a modern approach," Printince hall, 2010.

- [13] F. Glover and E. Taillard, "A user's guide to tabu search," Annals of Operations Research, vol. 41, 1993, pp 1-28.

- [14] X. Zhou and M. Zhong, "Bicriteria train scheduling for high-speed pas-J. Ende and M. Endog, "Difficult and endended in the formation of the proceed pairs senger railroad planning applications," European Journal of Operational Research, vol. 167, no. 3, 2005, pp. 752–771.

J. Freyberg, M. Walther, J. Wildberger and H. Wünsche, "Team Heispeed - Project Report," 2022. [Online]. Available: https://drive.

- [15] google.com/file/d/1KwNQX27NTHtL-JjdSbGBNHNb9Ana0EeU/view? usp=share link.

- [16] D. Hou and W. Zhang, "Multi-Warehouse Location of Logistics Based on Dijkstra and Divide-and-Conquer Algorithm," 2017 10th International Symposium on Computational Intelligence and Design (ISCID), 2017, pp. 442-447.

- [17] R. J. Dakin, "A tree-search algorithm for mixed integer programming problems," The Computer Journal, Vol. 8, 1965, pp. 250-255

## Comparison of Missing Data Imputation Techniques using Autoencoders

1<sup>st</sup> Rubaiya Kabir Pranti Communication Systems and Networks Cologne University of Applied Sciences Cologne, Germany rubaiya\_kabir.pranti@smail.th-koeln.de

3<sup>rd</sup> Sven Woehrle

Information and Communication Sciences Cologne University of Applied Sciences Cologne, Germany sven.woehrle@th-koeln.de

Abstract-Missing data in large-scale surveys reduces reliability in data analysis. Demographic and Health Surveys (DHS) are significant surveys including household information from which users can take valuable data insights for social activities and business purposes. DHS contain numerous missing values for various reasons. In this study, we aim to show a methodical comparison of autoencoder-based (AE) three techniques (simple autoencoder (AE), denoising autoencoder (DAE), and variational autoencoder (VAE)) which are advanced neural networks to impute missing values effectively with remarkable imputation results. For this purpose, we downloaded the raw datasets initially from the DHS'S website, from which we consider only household water supply information for our study. Before training the AE methods, we perform data pre-processing (including feature engineering), and exploratory data analysis to identify important features and then we transform the data to impute missing values precisely. We make the training dataset with complete data and generate artificial missingness in the test data and later we measure performance metrics from these variables. For evaluation purposes, we apply the k-fold cross-validation technique for five different missing ratios together with integrated hyperparameter regularization for improved imputation performance. Finally, the missing data are imputed on unseen test data after the final training of the autoencoders (AEs). In this regard, we analyze model performances using performance metrics such as root mean square error (RMSE) and visual inspection. Finally, we compare the performances of three AE-based imputation methods that provide expected imputation outputs. Especially, our study reveals that DAE provides better results compared to other two techniques (AE, VAE) in terms of RMSE, but VAE is more successful at determining all the underlying patterns and relationships of data features though RMSE values are higher than DAE's. Hence, AE falls behind DAE and VAE due to its simple architecture to capture patterns.

*Index Terms*—missing data imputation, autoencoders, deep learning, cross-validation, AE, DAE, VAE, DHS

#### I. INTRODUCTION

Using traditional missing data imputation methods such as mean and method imputation methods for handling missing data alone are insufficient techniques to deal with this issue. By building sophisticated neural network architectures, 2<sup>nd</sup> Gernot Heisenberg Information and Communication Sciences Cologne University of Applied Sciences Cologne, Germany gernot.heisenberg@th-koeln.de

trained under carefully designed loss functions, state-of-the-art models obtain impressive performance [1]. Therefore, in this study, we execute artificial neural networks (ANN) named as autoencoders including AE, DAE, and VAE for the effective imputation of missing data to address the problem.

Firstly, simple/regular AE, this deep neural network has latent space in between the input data and output data. AE is trained to minimize the reconstruction loss between the input and output data. For our missing data imputation tasks, AE primarily learns the internal correlations from the complete input training dataset. After learning from the training process, missing values are imputed on unseen test dataset with the help of learned representation during the training phase.

DAE, on the other hand, is a more effective approach than traditional AE (baseline) where noise is incorporated into input data. Then reconstruction of the input data is possible from the latent representation. In our research, DAE is trained on complete corrupted data where gaussian noise is added to the input data. Therefore, DAE learns to denoise or reconstruct the original data from the noisy input. DAE can considerably impute missing values more than simple AE.

Furthermore, VAE is a generative autoencoder that learns to reconstruct the input data and generate new data from the learned distribution. By following this, VAE fills in the missing values because of its homogeneity where we can sample from the latent space much smoother and it can generate a more meaningful output from every sample data location. Variational autoencoder produces more diverse and realistic imputations than both DAE and AE.

The evaluation of the AE, DAE, and VAE methods primarily depends on the root mean square error (RMSE) metric. This metric is preferred due to its ability to provide an acceptable performance measure.

Based on the results of tests, the DAE has the best performance with mean RMSE, followed by VAE, where the simple autoencoder has higher mean RMSE values.

#### II. DATA RETRIEVAL PROCESS

DHS surveys gather information from eligible respondents by using various types of questionnaires. For our study, we focus on only household questionnaires (from sub-saharan africa region people) and concentrate on analyzing water supplyrelated features (https://dhsprogram.com/methodology/Survey-Types/DHS-Questionnaires.cfm). The household questionnaire related raw datasets are retrieved from the DHS program website [2]. Through proper pre-processing of data, a total of 970637 rows of values contain seventeen columns including three vital features named 'source of drinking water (simplified)', 'time to get to a water source (minutes)', and 'location of source for water' related to the water supply. After that, by executing the data pre-processing step on the final dataset, all records with missing values in the original survey dataset are deleted. By employing the feature engineering process, we only keep these mentioned three features. In this paper, we mention these features as 'Source', 'Time', and 'Location' in short. These three columns have a correlation with each other. For instance, if the 'Time' column has a value of 0 minutes, the 'Location' column must have location features such as 'in own dwelling' or 'in own yard/plot'. But, if the 'Time' column contains more than 0 minutes, the 'Location' column has to provide 'elsewhere' category as mandatory relationships. In this way, the resulting dataset with fully known observations contains 679187 rows of data which are classified into fifteen different categories in the 'Source' column, three different categories in the 'Location' column, and minutes ranging from 0 to 1000 minutes in the 'Time' column.

#### III. METHODOLOGY

#### A. Data Pre-processing

We assess data pre-processing to identify crucial features and transform the data to enhance the effectiveness of the AEbased methods. For the next step, we use the cleaned dataset as input for the autoencoder-based imputation methods (AEs).

#### B. Feature Engineering

We conduct feature engineering to reduce the dimensionality of the dataset. In our case, the relevant features are named in short as Source, Time, and Location features.

#### C. Splitting Dataset

The dataset is divided into training and testing sets using a random split of 80% for training and 20% for testing. We use the training dataset to train the AEs, the validation dataset with missing values for validation purposes and the testing set with missing values to evaluate the performance.

#### D. Training Methods

We train three autoencoder-based methods during the training procedure using TensorFlow and Keras by customizing the architecture, loss function, and optimizer and by adding regularizer and initializer to specific layers which differ for these three methods.

#### E. Evaluation through Cross-Validation

The evaluation criteria for imputing missing values take root mean square error (RMSE) as a measure [3]. For better evaluation, we perform cross-validation to get an estimation of the performance of our deep learning methods through RMSE (reconstruction loss). Here, we apply k-fold cross-validation on the train folds, and later we obtain imputed data from test folds.

#### F. Hyperparameter Optimization

We execute hyperparameter regularizations for all three AEs (simple AE, DAE, VAE). Though, it is not recommended to use more layers and nodes to avoid complexity and increased time costs, still, for analysis purposes, different combinations of complex architecture with different bottleneck nodes are investigated with fixed steps which allows a precise standard of symmetry between the encoder and decoder, which is beneficial for the learning process [4]. To prevent overfitting in the AE and DAE, we integrate L2 regularizer. As an optimizer, we use the Adam optimizer. For activation function, ReLU (Rectified Linear Unit) was proven to be the most effective one. Another hyperparameter used in our AE methods is the He uniform initializer for initializing weights in the neural network layers. Additionally, for every autoencoder method, we chose an epoch size of 50 for time and resource constraints.

#### IV. MISSING VALUE IMPUTATION

#### A. Experimental Setup

To evaluate our methods, we clean (without any missing values) the dataset as the first step with some additional cleaning of unexpected rows. We also carry out label encoding on the cleaned and complete dataset. Then, we split the dataset into training, test, and validation set. Later, we introduce artificial missingness to the test set. Then, the mode imputation method (most frequently observed values in the dataset) fills the missing values in the test dataset temporarily before applying autoencoders as AEs should not be trained with NaN values. Therefore, we introduce the AE and its variants' networks and compile these with some configurations. These above-mentioned steps are repeated again within the k-fold cross-validation process. The RMSE is calculated between the actual (ground truth) values and imputed values. We estimate average RMSE by employing 5-fold cross-validation for each missing ratio 10%, 20%, 30%, 40%, and 50% by averaging the results between the 5 folds [5]. After getting the results for five different missing ratios, the unbiased examination is completed through a cross-validation technique to see how the AEs will perform on unseen test data. Then we train the AEs again as the final assessment step. Next, the AE techniques predict and impute missing values on the unobserved test dataset to assure AEs' real-world performance [6].

#### B. Evaluation Metrics

For our research project, we have mainly selected the Root Mean Squared Error (RMSE) metric and scatter plots to evaluate and compare the performance of different AEs in handling missing values. Here, RMSE can give a precise understanding of the deviation between ground truth values and imputed values. To assess the variability of the average RMSE values, the standard error of the mean RMSE and the confidence interval of the RMSE are calculated using the standard error. In this case, a 95% confidence interval is computed, which is based on a z-score of 1.96.

#### V. OVERALL COMPARISON

In this section, we compare the overall results for the DHS dataset regarding missing data imputation with the help of a 5-fold cross-validation process separately for every AEs such as regular AE, DAE, and VAE (Table 1.). And then we also present inconsistent results and performance (Table 2.).

#### A. Discussion on the Tables

From Table 1., for missing ratios (from 10% to 50%), we can observe that Denoising Autoencoder (DAE) is superior in most cases across various architectures upon understanding the underlying patterns and relationships well, exhibiting lower RMSE values than the other two AEs. Besides, we find that VAE and DAE outperform AE steadily for all architectures. And in certain cases, VAE even surpasses DAE and AE.

From Table 2., we see that there have been some inconsistencies and unrecognized patterns in the output of AE, DAE, and VAE methods. We acknowledge that for some rows, AEs have imputed missing values incorrectly as the location with 'elsewhere' label having time equals 0 minutes which does not match with the original training data. In this way, some rows are not acceptable though the RMSE values are lower. Regarding variational autoencoder (VAE), it outperforms other AE and DAE for some architectures except for (128,10) architecture. VAE has been always uniform with stable results without any contradictory output as earlier mentioned. But for VAE, RMSE values are higher than DAE in the majority of cases. For DAE, there are also evident inconsistent rows found, but the RMSE values are comparatively lower than the other two AE methods which makes it the optimal method for our dataset [7].

| Architecture | M. Ratio  | Comparison (RMSE Result) |

|--------------|-----------|--------------------------|

| (64,5)       | 10% - 50% | VAE > DAE > AE           |

| (64,10)      | 10% - 50% | DAE > VAE > AE           |

| (128,5)      | 10% - 50% | DAE > VAE > AE           |

| (128,10)     | 10% - 50% | DAE > AE > VAE           |

| (256,5)      | 10% - 50% | VAE > DAE > AE           |

| (256,10)     | 10% - 50% | DAE > VAE > AE           |

Table 1. Performance Comparison for different architectures

#### DETAILED INDIVIDUAL AUTOENCODER RESULTS

The following tables are regarding Table 3. to Table 5. which actually demonstrate the performance of the AEs in terms of missing data imputation considering 'Time' feature only. We compute missing data imputation tasks using three different Autoencoder approaches (AEs), the tables depict the

| Architecture | AE             | DAE                  | VAE            |

|--------------|----------------|----------------------|----------------|

| (64,5)       | 11786 rows     | 279 rows             | 21 rows        |

| (64,10)      | 585 rows       | 319 rows             | 0 rows         |

| (128,5)      | 17 rows        | 504 rows             | 0 rows         |

| (128,10)     | 11486 rows(UL) | 11090 rows(UL)       | 12176 rows(UL) |

| (256,5)      | 10898 rows     | 0 rows( <b>UI</b> .) | 4 rows         |

| (256,10)     | 0 rows(UI.)    | 902 rows             | 0 rows         |

Table 2. Inconsistent and Unrecognized Results Comparison for Different Architectures for Missing Ratio=30%, where UI=Unidentified Patterns

average RMSE values through 5-fold cross-validation (for missing ratios ranging from 10% to 50%). It should be noted that a lower RMSE value represents better performance. We also observe that all methods perform worse as the missing rate increases, which is to be expected because a dataset with a higher missingness proportion is also harder to impute [6]. Due to time constraints, we focused on evaluating the bottleneck layer with 5 and 10 nodes only for each AE method, considering only three features.

#### B. Imputation Results of Regular AE

Table 3. represents the RMSE results with uncertainty measures of a 5-fold cross-validation process for regular AE for the time column. The architecture combination (64, 10) performs acceptably. It can be concluded that when the bottleneck layer has fewer nodes, AE struggles to capture all key patterns in the input data.

#### C. Imputation Results of DAE

Table 4. displays the RMSE results with uncertainty measures for DAE using a 5-fold cross-validation process for the time column. Among the architecture combinations, (64,5) shows poor performance, characterized by higher RMSE values and inconsistent rows. Specifically, they only capture the Tubewell or borehole label in the source column and incorrectly identify the location as elsewhere with 0 minutes. These outputs fail to capture many significant patterns and result in higher RMSE values. The most meaningful architectures are again (64,10) like AE.

#### D. Imputation Results of VAE

For VAE, Table 5. shows RMSE results with uncertainty measures using a 5-fold cross-validation process for the time column. VAE is good at supplying more consistent outputs than AE and DAE. But RMSE values can be seen higher in most cases. Almost all architectures are acceptable for the VAE method for its consistency, except the (128,10) combination which deals with many unidentified patterns (only captured source= Tubewell or borehole and location= elsewhere with 0 minutes) by leaving many significant patterns (Table 2) in outputs with higher RMSE values.

#### CONCLUSION

In this study, we worked on missing data imputation tasks using AE, DAE, and VAE methods in the DHS dataset. In

| Architecture | Bottleneck | 10%         | 20%          | 30%          | 40%          | 50%          |

|--------------|------------|-------------|--------------|--------------|--------------|--------------|

| 64           | 5          | 9.737±0.720 | 12.994±0.677 | 16.302±0.784 | 18.468±0.706 | 20.256±0.343 |

| 64           | 10         | 9.715±0.729 | 12.934±0.669 | 16.199±0.788 | 18.330±0.704 | 20.076±0.333 |

| 128          | 5          | 9.752±0.712 | 13.008±0.671 | 16.289±0.784 | 18.421±0.703 | 20.189±0.333 |

| 128          | 10         | 9.711±0.728 | 12.936±0.672 | 16.248±0.793 | 18.380±0.708 | 20.126±0.336 |

| 256          | 5          | 9.743±0.722 | 12.996±0.666 | 16.278±0.782 | 18.415±0.700 | 20.167±0.333 |

| 256          | 10         | 9.707±0.725 | 12.922±0.667 | 16.186±0.789 | 18.317±0.706 | 20.066±0.334 |

Table 3. Average RMSE Results for Autoencoder (Time)

| Architecture | Bottleneck | 10%         | 20%          | 30%          | 40%          | 50%          |

|--------------|------------|-------------|--------------|--------------|--------------|--------------|

| 64           | 5          | 9.343±0.455 | 12.439±0.817 | 15.439±0.451 | 18.160±0.427 | 20.191±0.713 |

| 64           | 10         | 9.104±0.775 | 12.917±0.634 | 15.966±0.438 | 17.870±0.208 | 19.707±0.900 |

| 128          | 5          | 9.104±0.775 | 12.920±0.632 | 15.964±0.437 | 17.874±0.209 | 19.707±0.899 |

| 128          | 10         | 9.104±0.776 | 12.916±0.631 | 15.964±0.436 | 17.872±0.211 | 19.710±0.897 |

| 256          | 5          | 9.099±0.775 | 12.919±0.632 | 15.967±0.435 | 17.877±0.210 | 19.712±0.898 |

| 256          | 10         | 9.103±0.773 | 12.923±0.628 | 15.970±0.425 | 17.877±0.211 | 12.923±0.628 |

| Table 4. Average RMSE Results for Denoising Autoen |

|----------------------------------------------------|

|----------------------------------------------------|

| Architecture | Bottleneck | 10%           | 20%           | 30%          | 40%          | 50%          |

|--------------|------------|---------------|---------------|--------------|--------------|--------------|

| 64           | 5          | 9.721±0.724   | 12.938±0.669  | 16.212±0.788 | 18.353±0.701 | 20.129±0.354 |

| 64           | 10         | 9.725±0.726   | 12.941±0.668  | 16.213±0.784 | 53.712±0.726 | 20.104±0.333 |

| 128          | 5          | 9.722±0.726   | 12.953±0.656  | 16.210±0.790 | 18.349±0.700 | 20.099±0.334 |

| 128          | 10         | 18.284±15.370 | 12.943±0.6677 | 16.216±0.786 | 18.354±0.703 | 20.109±0.346 |

| 256          | 5          | 9.728±0.734   | 12.942±0.672  | 16.261±0.785 | 18.348±0.704 | 20.093±0.332 |

| 256          | 10         | 9.722±0.725   | 12.941±0.668  | 16.215±0.791 | 18.348±0.706 | 20.099±0.339 |

#### Table 5. Average RMSE Results for Variational Autoencoder (Time)

this regard, we extended the existing deep learning architectures by introducing specific hyperparameter optimizations that are well-fit for particular scenarios. We investigated various missing rates during the cross-validation process. Our experiments consistently showed that DAE outperformed the other AE methods in all aspects. Therefore, DAE surpassed other methods due to the little effect of the noise. In contrast, VAE had higher RMSE values than DAE because it was strongly affected by hyperparameters. However, when it comes to generating consistent (valid) imputations, the VAE exceeds both the DAE and AE architectures.

#### REFERENCES

- [1] Śmieja, Marek, Maciej Kolomycki, Łukasz Struski, Mateusz Juda, and Mário Figueiredo. "Iterative Imputation of Missing Data Using Auto-Encoder Dynamics." In Iterative Imputation of Missing Data Using Auto-Encoder Dynamics, 258-269. 2020. doi:10.1007/978-3-030-63836-8\_22.

- [2] Abubakar, Ismaila Rimi. 2017. "Access to Sanitation Facilities among Nigerian Households: Determinants and Sustainability Implications" Sustainability 9, no. 4: 547. https://doi.org/10.3390/su9040547.

- [3] Gaudette, L., Japkowicz, N. "Evaluation Methods for Ordinal Classification." In Advances in Artificial Intelligence. Canadian AI 2009, edited by Y. Gao and N. Japkowicz, Lecture Notes in Computer Science(), vol. 5549. Springer, Berlin, Heidelberg, 2009. https://doi.org/10.1007/978-3-642-01818-3\_25.

- [4] Pereira, R.C., Santos, M., Rodrigues, P., Henriques Abreu, P. (2020). "Reviewing Autoencoders for Missing Data Imputation: Technical Trends, Applications and Outcomes." Journal of Artificial Intelligence Research 69 (2020): 1255-1285. doi:10.1613/jair.1.12312.

[5] Psychogyios, K., Ilias, L., and Askounis, D. "Comparison of Missing

- [5] Psychogyios, K., Ilias, L., and Askounis, D. "Comparison of Missing Data Imputation Methods using the Framingham Heart study dataset." In 2022 IEEE-EMBS International Conference on Biomedical and Health Informatics (BHI), Ioannina, Greece, 2022, pp. 1-5. doi:10.1109/BHI56158.2022.9926882.10.1109/BHI56158.2022.9926882.

- [6] Psychogyios, K., Ilias, L., Ntanos, C., and Askounis, D. "Missing Value Imputation Methods for Electronic Health Records." IEEE Access 11 (2023): 21562-21574. doi:10.1109/ACCESS.2023.3251919.

- [7] Ryu, S., Kim, M., Kim, H. "Denoising AutoencoderBased Missing Value Imputation for Smart Meters." IEEE Access 8 (2020): 40656-40666. doi: 10.1109/ACCESS.2020.2976500.

# FPGA-based acceleration of neural net simulation

Felix Sebastian Nitz TH-Koeln, University of Applied Science Cologne, Germany felix.nitz@smail.th-koeln.de

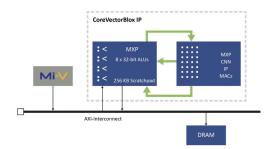

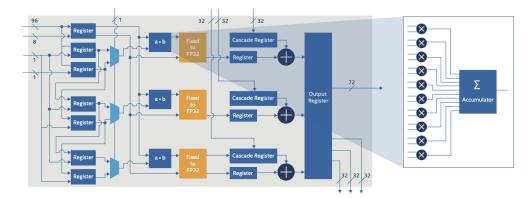

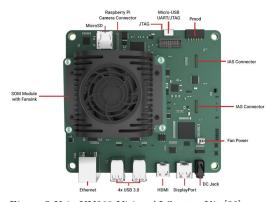

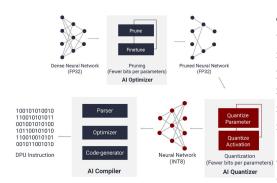

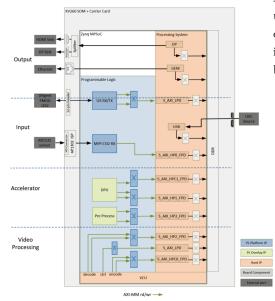

Abstract—The widespread integration of Artificial Intelligence (AI) in both Industry 4.0 and personal life necessitates an objective examination of the factors driving its adoption. This study explores modern hardware designed to accelerate AI applications, which plays a crucial role in optimizing AI performance. The article categorizes AI accelerators into two types: centralized and edge accelerators. Centralized accelerators, such as Graphics Processing Units (GPUs) and Tensor Processing Units (TPUs), focus on large-scale data centers and are utilized for cloud-based AI tasks. Conversely, edge accelerators, exemplified by Multiprocessor Systems-on-Chips (MPSoCs) with a Field Programmable Gate Arrays (FPGAs)-part, are intended for decentralized applications that necessitate prompt outcomes similar to those observed on smartphones or robots. The paper presents an in-depth examination of the techniques and characteristics utilized in both areas, with a focus on the enhancement of AI in the edge domain through FPGA technology. A closer look at the FPGA-based edge reveals that Intel is currently the only vendor using dedicated hardware for AI acceleration. Other manufacturers are focusing on reconfiguring existing hardware by enhancing the interface between a Central Processing Unit (CPU) and an FPGA in one device.

Index Terms—Machine Learning, Deep Learning, ASIC, FPGA, MPSoC, Decentralization, AI acceleration, AI on edge, Centralized AI, Energy Efficiency

#### I. INTRODUCTION

Since Artificial Intelligence (AI) is increasingly important in both the Industry 4.0 movement and our personal lives, it is intriguing to examine the reasons behind its profitability. Public acceptance and interest in AI- based products, ranging from autonomous driving to rice cookers with fuzzy control, are a contributing factor [34]. An AI-based system can significantly improve a product's efficiency, safety, and usability [1] [2]. To achieve optimal performance, modern hardware is crafted specifically for accelerating AI-driven applications [35]. As stated by Synopsis, an AI accelerator is a high-performance parallel computing machine designed to efficiently process AI workloads, including DL [3]. There are two main spaces for accelerating AI-based operations: Centralized and edge computations. The first approach involves using large, centralized data centers to either train neural networks or deploy massive AI-based services. Examples of this include voice assistants in smart homes and the advancements in cloud based training of AI-based tasks like autonomous driving [4]. The edge represents the second main space. Its application requires an almost immediate outcome, such as for interactive programs used on smartphones or robots. Due to this decentralized function, energy efficiency and compact size are key factors.

This paper evaluates potential hardwarebased methods for accelerating AI-based tasks. It begins by outlining the main characteristics of the two main spaces and describing the methods used to accelerate AI processes at the hardware level. The focus then shifts to an edge space example, featuring a practical experiment on Field Programmable Gate Array (FPGA)based AI acceleration. Finally, this study compares the two main spaces, with a particular emphasis on FPGA technology as a represen-

#### II AI accelerator main spaces

tative of edge computing. The research aims to determine the relative capabilities of each space.

#### II. AI ACCELERATOR MAIN SPACES

As previously stated, AI accelerators can be divided into two main areas: The centralized and the edge accelerators. To enhance comprehension of each space, a representative will be used to explain them individually. Considering the latest industry advancements in centralized accelerators, apart from supercomputers, this paper will concentrate on Graphics Processing Units (GPUs) and Tensor Processing Units (TPUs) as representatives of this category. In the edge computing realm, FPGAs serve as proxies due to their multiplexing capabilities, compact form factor, and wide availability, making them powerful computing tools. [36].

The centralized space of AI acceleration focuses on the clustering of processor units, most commonly of the graphics or tensor type [35] [37]. These units are frequently utilized for cloud-based applications or in data centers. Initially, Graphics Processing Units were used due to their availability and computing power. Subsequently, companies such as Nvidia and AMD began developing new types of GPUs that could accelerate AI-related operations at the hardware level. This was achieved through the optimization of communication between CPUs and GPUs, creating a specialized computing path for AI-related tasks. The introduction of CUDA and the resulting improvements in parallel computing tasks within a single GPU have accelerated AI-based operations [39]. Through further developments of CUDA, an enhanced acceleration could be attained through crosstalk between multiple GPUs and by intelligently assigning tasks to each unit. This configuration enables an increase in both compute and memory bandwidth, resulting in a significant acceleration of AI-specific tasks [35]. Additionally, implementing the IEEE 754 standard for Floating Point (FP) arithmetic in GPUs has further enhanced precision and speed [5] [6] [7]. By increasing the number of Arithmetic Logic Units (ALUs), the GPU can execute multiple multiplications and additions simultaneously. In addition, Floating-Point Units (FPUs) were introduced as FP or single precision units to the GPUs. An FPU is a specialized logic unit that directly performs arithmetic operations with Floating-Point values [40]. FPUs have been present in CPUs since the 1990s [8]. However, because of increased power and space requirements, they were only implemented in GPUs through the adoption of IEEE 754 in 2008 [9]. This, in turn, has accelerated AI tasks utilizing GPUs.